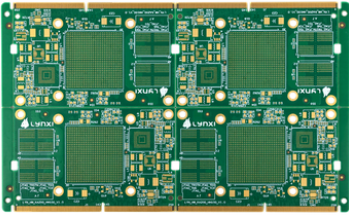

在電(diàn)子工(gōng)程領域,高速PCB闆設計是一個繞不過去的話題。随着電(diàn)子産(chǎn)品對速度和性能(néng)的要求日益增加,高速PCB設計技(jì )術也成為(wèi)了電(diàn)子工(gōng)程師必須掌握的技(jì )能(néng)。但是,在高速PCB闆設計中(zhōng),工(gōng)程師們需要注意哪些關鍵事項呢(ne)?

1. PCB布線(xiàn)設計:确保效率和性能(néng)

談到高速pcb闆設計注意事項,高速PCB布線(xiàn)設計是确保整闆性能(néng)的關鍵。首先,工(gōng)程師們需要确保布線(xiàn)路徑的合理(lǐ)性,避免過長(cháng)的走線(xiàn)或是過多(duō)的轉彎。

同時,對于高頻信号,特别是超過1GHz的信号,微帶線(xiàn)和帶狀線(xiàn)的選擇與設計尤為(wèi)關鍵。另外,布線(xiàn)密度、線(xiàn)寬、線(xiàn)距都應根據電(diàn)路的實際要求進行優化,以減少串擾和幹擾。

2. 信号完整性的确保:避免信号失真

信号完整性是高速PCB設計中(zhōng)的另一個核心話題。為(wèi)确保信号在傳輸過程中(zhōng)不會受到幹擾或失真,需要考慮到信号回流路徑、參考平面以及終端匹配等因素。

适當地使用(yòng)終端和源端阻抗匹配,結合恰當的布線(xiàn)策略,可(kě)以有(yǒu)效地減少信号反射、串擾和環路。

3. 如何抑制電(diàn)磁幹擾:保障系統穩定性

電(diàn)磁幹擾(EMI)是高速PCB設計中(zhōng)不可(kě)忽視的問題。為(wèi)了抑制電(diàn)磁幹擾,設計中(zhōng)應确保良好的接地策略,如使用(yòng)大面積的接地銅皮、短接地回路等。此外,合理(lǐ)的布局、屏蔽關鍵部件以及控制電(diàn)源噪聲,也都對抑制電(diàn)磁幹擾起到關鍵作(zuò)用(yòng)。

4. 高速差分(fēn)信号對布線(xiàn):提高信号質(zhì)量

高速差分(fēn)信号對布線(xiàn)在高速PCB設計中(zhōng)具(jù)有(yǒu)重要意義。差分(fēn)布線(xiàn)可(kě)以提高信号的抗幹擾能(néng)力,但它的布線(xiàn)要求較為(wèi)嚴格。

需要确保兩條線(xiàn)的長(cháng)度、線(xiàn)寬和間距都完全相同,避免因長(cháng)度或者走線(xiàn)不同導緻的時間偏差。正确的差分(fēn)布線(xiàn)可(kě)以大大提高信号質(zhì)量,減少信号幹擾。

總之,高速pcb闆設計注意事項涉及多(duō)方面的知識和技(jì )巧,從PCB布線(xiàn)設計到信号完整性的确保,再到電(diàn)磁幹擾的抑制和高速差分(fēn)信号對布線(xiàn),每一環節都需要工(gōng)程師們細心鑽研和實踐。